随着集成电路密度提高,晶体管的工艺节点不断微缩,已逼近物理极限。三维互补式场效应晶体管(3D CMOS)技术成为破局的潜在路径。传统硅基3D CMOS集成技术热预算较高,导致工艺复杂成本提高,并可能引发性能退化等问题,限制了其商业应用。

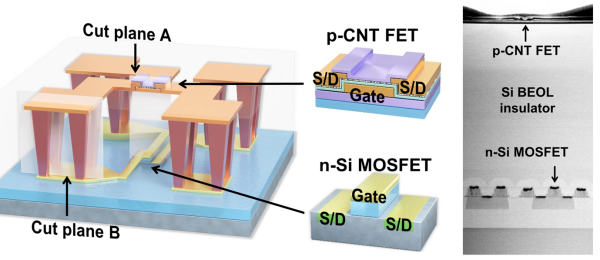

针对上述问题,中国科学院微电子研究所研究员李博与副研究员陆芃团队,基于碳纳米管材料低温成膜能力,提出碳纳米管/硅异质集成的3D CMOS技术,实现了180nm SOI器件后道的低温碳纳米管器件集成。该团队提出面向高性能数字电路应用的工艺优化方案,可实现碳纳米管器件阈值电压的精准调控,可完成N、P晶体管电学特性的匹配,使3D CMOS噪声容限提升,同时实现高增益、超低功耗和高均一性等优异性能。

进一步,为论证这一述技术在先进工艺节点中的集成能力,团队使用TCAD仿真搭建了14nm FinFET/CNT 3D CMOS电路单元。理论分析显示,该技术在噪声容限和功耗方面优于商用14nm-FinFET工艺。

相关研究成果以Low-Thermal-Budget Construction of Carbon Nanotube p-FET on Silicon n-FET toward 3D CMOS FET Circuits with High Noise Margins and Ultra-Low Power Consumption为题,发表在《先进功能材料》(Advanced Functional Materials)上。该工作由微电子所、南京大学、安徽大学合作完成。

碳硅三维异质集成CMOS FET器件示意图

供稿人:杨越

审核人:文成锋